Our website is made possible by displaying online advertisements to our visitors.

Please consider supporting us by disabling your ad blocker.

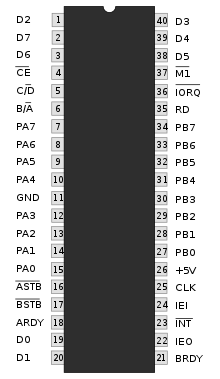

Z80 PIO

Die Parallel-Input/Output-Schnittstelle (kurz PIO) des Zilog-Z80-Prozessors organisiert die parallele Datenübertragung zwischen Mikrocomputer und den Peripheriegeräten. Die Aktivitäten des PIO-Schaltkreises werden ausschließlich durch den Hauptprozessor (central processing unit, CPU) gesteuert. Somit ist es notwendig, dass beide Schaltkreise miteinander Signale austauschen können.

Da ein Prozessor für mehrere Peripheriegeräte zuständig ist, empfängt er auch mehrere Interrupt-Signale, kann allerdings immer nur eines pro Zeiteinheit abarbeiten. Somit muss ein Prioritätsscheduling gewährleistet sein. Der interrupt requestor (also das den Interrupt anfordernde Gerät) muss dem System sowohl Beginn, als auch Ende seiner CPU-Inanspruchnahme signalisieren. Durch daisy chaining, also Verkettung, über die Anschlüsse Interrupt–Enable In (IEI) und Interrupt–Enable Out (IEO) können mehrere PIOs untereinander priorisiert werden.

- IEI (Interrupt-Enable In): Die PIO wird berechtigt, den Interruptvektor /INT an die CPU zu senden, wenn keine höher priorisierte PIO einen Interrupt aussendet.

- IEO (Interrupt-Enable Out): Der Interrupt wird bearbeitet, niedriger priorisierte PIOs müssen warten.

Betriebsarten:

- Mode 0: Byteweise Ausgabe

- Mode 1: Byteweise Eingabe

- Mode 2: Bidirektionale Ein- und Ausgabe

- Mode 3: Einzelbitsteuerung (zur bitparallelen Ausgabe von Steuersignalen)

Vom VEB Kombinat Mikroelektronik Erfurt wurde der Z80-PIO-Schaltkreis unter den Bezeichnungen UA, UB und UD 855 D als Teil des Mikroprozessorsystems MME U880 hergestellt.[1]

- ↑ Referenzfehler: Ungültiges

<ref>-Tag; kein Text angegeben für Einzelnachweis mit dem Namen semi1988.

Previous Page Next Page